# **Symmetric Stacking Counter Based Testing**

## S Chandrasekaran M.E

Lecturer Department Of Computer Engineering Ayyanadar Janakiammal Polytechnic College, Sivakasi, Tamilnadu Corresponding Author: S Chandrasekaran M.E

Abstract: Parallel counters are enter components in numerous number juggling circuits, particularly quick multipliers. Another paired counter plan is proposed. It utilizes Multiplexer (MUX) based full adder circuit, which aggregate the greater part of the "1" bits together. In proposed structure one xor obstruct in traditional snake is supplanted by multiplexer square with the goal that the basic way delay is limited. Counter-based systems have been proposed for use in worked in test set installing. A solitary counter or various counters might be utilized with one or different seeds. This paper concentrates on region productive blame tolerant full snake outline. This outline can repair single and twofold blame without intruding on the typical operation of a framework. A framework must be blame tolerant to diminish the disappointment rate in the blame area. In this approach self-checking full snake is utilized recognizing the blame in light of inside usefulness. The idea of self-checking and blame tolerant is acquainted with manage the issue of blame. Subsequently the operations associated with the proposed configuration is performed utilizing self-checking and mistake rectifying counter based full snake plan. Moreover, counters might be joined with Read Only Memory (ROM) proposed framework coded in Verilog Hardware Description language (VHD) and mimicked utilizing Xilinx 12.1.

**Keyword:** Multiplexer, Counter, Full adder, Fault tolerant, stacking, Read Only Memory (ROM);

Date of Submission: 07-10-2019 Date of acceptance: 22-10-2019

#### I. Introduction

A (n, m) parallel counter is a circuit which gives a m-bit tally of the quantity of the n-inputs that are rationale ONES. A counter contrasts from a compressor in that compressors have convey information sources and convey yields notwithstanding the "typical" data sources and yields, while counters don't have convey information sources and yields. The most broadly utilized parallel counters are full adders which are (3:2) counters and half adders which are (2:2) counters.

Bigger parallel counters are particularly helpful in the execution of generally utilized flag handling com-ponents, for example, multipliers, assembles, and so on. The speed of multipliers is a basic issue in deciding the execution of chip whatever is left of this con- cise presents the counters in area I. Next the related works and quick double counter utilizing symmetrical stack are considered in Area II. At that point, in Seg- ment III, the proposed is displayed. Segment IV shows an exploratory Outcomes and executioninves- tigation to outline the adequacy of the equipment se- curity approach. At long last, the conclusions are abridged in Segment V.

In this paper [1] segment pressure multiplier to outline a strategy for section limited by the compressor based multipliers. So the principle downside is the higher equipment multifaceted nature. Be that as it may, the Energy Delay Product (EDP) is marginally higher than the lower arranging compressors. Wallace Tree multiplier utilizing fast counter to be intended for the counter approach. This compressor utilizes counter property. With the goal that the yield of com- pressor gives number of 1's at input. So the principle disadvantage for defer overhead[2]. In the novel models took after by the Wallace Tree multiplier circuit. In this manner the effective (m,n) parallel counters are the fundamental mux counter then the mux based approach includes extra of the complex [3]. Bolster forward and criticism intercon- nections are inferred by the techniques utilized as a part of the aloofness for the interconnected inthe symmetrically disseminated framework. Alongthese lines the encourage forward techniques to be held at the steering multifaceted nature [4].

In the fast increase of 8-4 and 9-4 compressors uti- lizing the higher request of the compressor can be adequately utilized for rapid duplications. Subse- quently the augmentation is a crucial operation in the vast majority of the flag handling calculation [5]. In this paper took after by the fast operations of the full viper based counter. Along these lines the counter to be examined by the engineering of the Wallace multi- pliers. So the fundamental disadvantage for this paper utilizing high power utilization [6]. In the quick num- ber juggling circuits utilizing low power, low voltage (5:2) compressors cell. At that point the compressor cell is as needs be performed by low power compres- sors. In such manner numerous inventive outlines for essential rationale capacities utilizing pass transistors and transmission doors have showed up in the writing as of late. This may likewise brings about problematic operations as the power supply voltage is downsized. Subsequently the 16

transistor included cell (16T) given isn't a decent decision for low voltage operations [7].

The piece of discovery and gathering techniques utilizing multi-scale symmetric. It's recuperating and gathering symmetric parts [8]. In this paper to outline a proficient reversible multiplier utilizing leather treated Energy Delay Adder (EDA). In this way the strategy can be executed as low power planning by reversible rationale entryways. So it can be possess the substantial information, yield necessities [9]. Feed forward and feedback interconnections are derived by the methods used in the passivity for the intercon- nected in the symmetrically distributed system. Ac- cordingly the encourage forward techniques to be held at the steering multifaceted nature [4]. In the rapid duplication of 8-4 and 9-4 compressors utilizing the higher request of the compressor can be adequately utilized for fast augmentations. Thus the multiplica- tion is a fundamental operation in most of the signal processing algorithm [5]. In this paper followed by the high speed operations of the full adder based counter. Thus the counter to be analyzed by the architecture of the Wallace multipliers. So the main drawback for this paper using high power consumption [6]. In the fast arithmetic circuits using low power, low voltage (5:2) compressors cell. Then the compressor cell is accordingly performed by low power compressors. In this regard many innovative designs for basic logic functions using pass transistors and transmission gates have appeared in the literature recently. This may also results in unreliable operations as the power supply voltage is scaled down. Hence the 16 transistor added cell (16T) given is not a good choice for low voltage operations [7]. The part of detection and grouping methods using multi-scale symmetric. It's recovering and grouping symmetric parts [8].

In this paper to design a efficient reversible multiplier using tanner EDA. Thus the method can be performed as low power designing by reversible logic gates. So it can be occupy the large input, output requirements [9]. In this paper, an advanced configuration for a symmetric multilevel voltage source inverter is pro- posed [10]. The proposed inverter is able to generate the nine levels using a lower number of circuit devices including power semiconductor switches. More- over, the reduced amount of on-state switches in the suggested configuration decreases voltage drops. Power losses are diminished, the given simulation results confirm the feasibility of the proposed config- uration. To approve the practicability of the proposed inverter, a prototype of the proposed topology has been implemented [11]. Finally, simulation results show that the obtained results are in good agreement. As a result, the total cost is considerably reduced, and the control scheme getssimpler. In this work, changing the internal equations yields a new realization with a 6 XOR delay. In another structure has been disclosed, the critical path delay of which equals 7XORs. As seen, the counters in each gray polygon build a 4:2 compressor. Comparing the proposed implementation [12] with this architecture indicates that our implementation has less intercon- nections and XOR delays. It moreover reduces the number of stages required for eliminating carry prop- agation delay from 3 stages to 2. This work presents a 1.2-ns16×16-Bit Binary Mul-tiplier Using High Speed Compressors [13].

Forhigher request duplications, an enormous number of adders or compressors are to be utilized to play outthe incomplete item expansion. We have lessened the quantity of adders by presenting exceptional sort of adders that are skilled to include five/six/seven bits for each decade. These adders are called compressors. Twofold counter property has been converged with the compressor property to grow high request com-pressors. Employments of these compressors allow the decrease of the vertical basic ways. A  $16\times16$  piecemultiplier has been produced utilizing these compressors. These compressors make the multipliers quickerwhen contrasted with the ordinary outline that have been utilized 4-2 compressors and 3-2 compressors. New implementation for 7:2 compressors, based on the conventional architecture, is proposed. According to the results, the design presented achieves a remark- able improvement in terms of speed (especially in low voltages) and power consumption over the best coun-terpart [14].

By using the conventional 7:2 architecture as basis and changing its internal equations as follows, our proposed implementation (Figure 4) could achieve a better performance. In our novelty the critical path delay equals 6 XORs, which means the overall delay is reduced by one XOR as compared to the conven-tional counterpart. Applying the following changes to the above equations reduces the relation between the sum and carry generating trees and thuscauses. This paper proposes various designs for the coun- ter based Wallace multipliers to investigate their exe- cution for different piece lengths. Plans are blended utilizing Synopsys Design Compiler in 90 nm process innovation and the post union deferral and power comes about are gotten by utilizing Synopsys Prime Time [15]. The proposed counter based Wallace mul-tipliers are likewise contrasted with conventional Wallace multiplier with assess the vitality per task of the two plans. The combination comes about demon- strates that the Power-Delay Product of the counter based Wallace multiplier is up to 17% lower when contrasted with the customary Wallace multiplier. This paper [16] presents a Low-voltage low-con- trol CMOS full stack. Low power plan of VLSI cir- cuits has been distinguished as a basic innovative need lately because of the popularity for versatile shopper gadgets items. In such manner numerous cre- ative outlines for essential rationale capacities utiliz- ing pass transistors and transmission doors have showed up in the writing as of late. These plans de-pended on the instinct and astuteness of the fashion- ers, without including formal outlinemethodology.

## **II.** Counter implementation

Much of the time, the outline of (7:3) parallel counter is appeared. By and large such counters are sufficiently expansive to outline the ideas without getting hindered with an excessive amount of detail. Now and again, counters of different sizes are ap-peared to show the technique.

The limit entryway counters multipliers incorpo- rated a plan for a (7:3) counter executed with transforming edge doors gives a meaning of upsetting edge entryways. There are n twofold data sources, each with a comparing weight. On the off chance that the total of the weights of the information sources that are rationale ONES surpasses the edge of the entryway the yield is a rationale ZERO, generally the yield a rationale ONE. At that point the acknowledgment of a (7:3) parallel counter with three reversing limitdoors.

This circuit utilizes three limit doors with seven, eight and nine information sources and edges of four, six and seven, separately. The postponement of the slightest huge piece of the tally,  $y_2$ , is three door de-lays, the deferral of the center piece,  $y_1$ , is two entry- way delays, and the deferral of the most huge piece,  $y_0$ , is one entryway delay. This approach has not been generally utilized, maybe due to the trouble of ac- knowledging huge edge doors with exact limits.

This counter in view of an exchanging tree actual- ized with transfers expressed to be an expansion of a thought that is because of Falk off. The main counter information controls a solitary shaft twofold toss transfer, the second info controls a twofold post two- fold toss hand-off, the third information controls a triple post triple toss hand-off, and so forth. The intri- cacy of this approach develops as the square of the quantity of sources of info, making the cost restrictive for the acknowledgment of huge counters. The hand-off switches can be actualized with su- perconducting cryotrons. In VLSI, CMOS domino rationale is additionally reasonable for the acknowl- edgment of exchanging tree. Exchanging trees for the three bits of a (7:3) parallel counter. The acknowl- edgment of the exchanging trees with domino ra- tionale. Albeit customary outline tenets would not permit the same number of levels of transistors be- tween the  $V_{\rm dd}$  and  $V_{\rm ss}$  supplies as the eight levels of this circuit, reenactments demonstrate that execution of the structure does not endure.

Cultivate and Stockton built up a counter actualized with full and half adders. This techniques (31:5) par- allel counter which comprises of collection the coun- ter contributions to [n/3] sets of three lines every which are contribution to full adders (where: [x] signi- fies the biggest whole number not exactly or equivalent to x). The [n/3] whole and [n/3] convey yields of the full adders (and any natural contributions to the counter) are assembled into threes and connected to second (littler) arrangements of full adders, and so on. The quantity of full adders to understand a (n, m) par- allel counter is inferred as not exactly or equivalent to n.

The deferral for the slightest critical piece of the tally is m-1 full snake delays (accepting that the postponement from any contribution to any yield of a full viper is 1 full snake delay) and the deferral for the most noteworthy piece of the check is 2m-3 full viper delays. It is shown that the parallel adders can then again be acknowledged with quick adders. It was recommended that read no one but recollections could be utilized; yet convey look ahead adders or contingent whole adders would be a more proper decision with current innovation. In the event that the parallel viper has postpone practically identical to a full snake delay, this approach gives all bits of a (n, m) parallel counter in m-1 full snake delays.

### III. Solution methodology

A double counter plan is proposed. It utilizes 3-bit stacking circuits, which assemble the greater part of the "1" bits together, trailed by a novel symmetric technique to consolidate sets of 3-bit stacks into 6-bit stacks. The bit stacks are then changed over to paired checks, creating 6:3 counter circuits with no xor en- tryways on the basic way. This shirking of xor doors brings about quicker outlines with productive power and territory use.

In VLSI reenactments, the proposed counters are speedier than existing parallel counters and furthermore devour less power than other higher request counters. Furthermore, utilizing the proposed counters in existing counter-based Wallace tree multiplier models decreases inertness and power utilization.

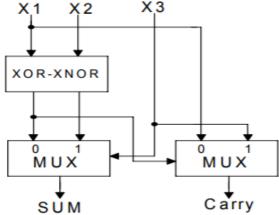

Figure.1 shows the fundamental full stack circuit. It can be utilized ordinary counter for the plan. They

arehaving XOR-XNOR for the info X1, X2 and X3 is associated by the immediate contribution for mux.

Figure 1 Conventional counter

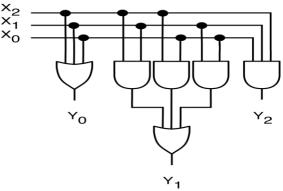

Figure 2 Three-bit stacker circuit

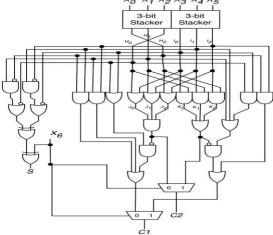

Figure 3 7:3 Counters based on symmetric stacking

Essential full adder circuit. It can be utilized tradi- tional counter for the plan. They are having XOR-XNOR for the information X1, X2 and X3 is associ- ated by the immediate contribution for mux. The customary counter outlines gives from whole and convey yield.

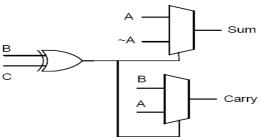

The proposed changed full stack circuit as appeared in Figure 4. It comprises of two 2:1 MUX and a XOR entryway. In the proposed structure, one XOR ob- struct in the regular full viper is supplanted by a mul-

tiplexer square with the goal that the basic way delay is limited. As can be seen, the basic way delays. (i.e.) delay= XOR + MUX

three yields  $Y_0$ ,  $Y_1$ , and  $Y_2$  to such an extent that the quantity of "1" bits in the yields is the same as the quantity of "1" bits in the information sources, yet the "1" bits are assembled together to one side took after by the "0" bits. Unmistakably the yields are then shaped by,

$$Y_0 = X_0 + X_1 + X_2$$

$$Y_1 = X_0 X_1 + X_0 X_2 + X_1 X_2 \ Y_2 = X_0 X_1 X_2.$$

Specifically, the main yield will be "1" if any of the sources of info is one, the second yield will be "1" if any two of the information sources are one, and the last yield will be one if every one of the three of the data sources are "1." The  $Y_1$  yield is a lion's share work and can be executed utilizing one complex CMOS door. Figure 3 shows the symmetric stacking technique can be utilized to make a 7:3counter too.

Figure 4 Proposed Full Adders

The Proposed full adders of the other two data sources are given to XOR entryway, the yield of which will go about as a select line to both the multi- plexers. The contributions of the second multiplexer are, the bits other than the convey bit.

This special method for outlining prompts the lessening of the ex- changing movement, which thus diminishes the power. What's more, the basic way delay is likewise decreased contrasted with the current outlines exam- ined in writing, which prompts diminishment in defer- ral and hence expanding the speed. Operation of the proposed full snake can be clarified as takesafter:

- a) When both B and C are zero or one, sum =A;

- b) When either of B or C is one and another is zero, sum=A;

- c) When both B and C are zero or one, carry=B; When either of B or C is one and another is zero, carry=A;

This can be implemented by using second MUX with XOR output as selection line. Since XOR employs most of the power consumption in the adder circuit, by reducing number of XOR gates, power consumption of the full adder can be reduced. The proposed full adder is applied into array multiplier reduction stage to validate the effectiveness. In array structure the partial products is divided into certain levels. In each level, whenever there are three bits, full adder has to be used. Out of the three inputs, one input and its complement is provided as inputs to the firstmultiplexer.

## IV. Results and discussion

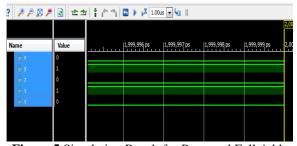

The Figure 5 demonstrates the results for simula- tion of proposed full adder network.

Figure 5 Simulation Result for Proposed Full Adders

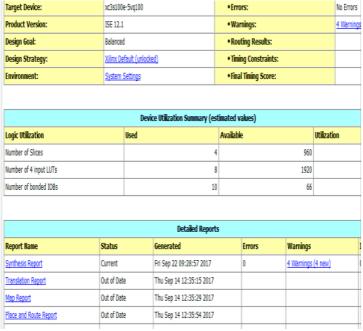

The Figure 6 demonstrates that plan outline of the proposed framework. It gives the assessed estimations of the capacity.

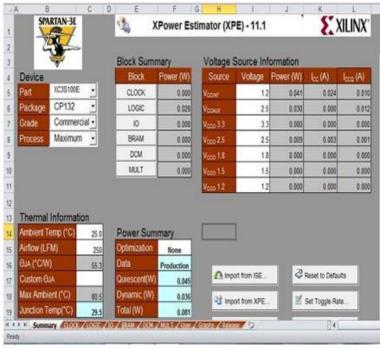

Figure 7 shows the Power examination of proposed framework is appeared in above fig 7. This investigation mostly focused on the number IOs in the whole framework to acquire the yield. In the whole framework, the accessible quantities of IOs are 12.0 and the IOs used to get the yield are 0.008. The aggregate accessible power in the framework is 0.081 W and thus the use of energy is 0.2 W.

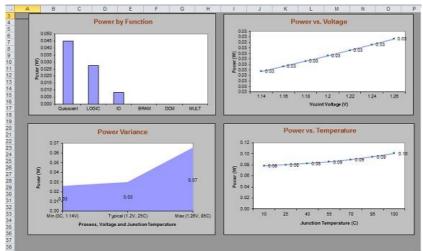

Figure 8. shows the Power New Full Adder (NFA) Counters the proposed has been reenacted and

theunion report can be acquired by utilizing Xilinx ISE 12.1i.

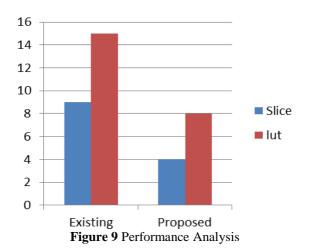

The Figure 9 given underneath is demonstrated that there is a significant lessening in time and zone in view of the execution comes about which have been finished by utilizing Simple 3 processor. The pro- posed calculation altogether lessens zone utilization when contrasted with the current framework.

Figure 6 Design Summary of .New Full Adder (NFA) Counters

The different parameters utilized for figuring ex- isting and proposed frameworks with Austere 3 processor are given in the Table.1

TABLE.1 COMPARISON OF EXISTING ANDPROPOSED SYSTEM

| L | S.NO | Parameter | Existing | Proposed |

|---|------|-----------|----------|----------|

| Γ | 1    | Slice     | 9        | 4        |

|   | 2    | LUT       | 15       | 8        |

Figure 7 Power Analysis New Full Adder (NFA)Counters of System

Figure 8 Power New Full Adder (NFA) Counters

V. Conclusion

In this paper, a plan strategy for region viable and speed effective counter is planned and reproduced. A twofold counter in view of a novel symmetric piece Aggregate and convey computation approach is pro-posed. We demonstrated that this tallying strategy can be utilized to actualize 6:3 and 7:3 counters, which can be utilized as a part of any parallel multiplier cir- cuit to include the fractional items. We showed that 6:3 counters actualized with this NFA system accom- plish higher speed than other higher request counter outlines while diminishing forceutilization.

S. Asif and Y. Kong (2015), "Design of an algorithmic Wallace multiplier Using high speed counters", in Proc. IEEE Comput. Eng. Syst. (ICCES),pp.133-138.

#### References

- C. S. Wallace (1964), "A suggestion for a fastmultiplier", IEEE Trans. Electron. Comput. vol. EC-13, no. 1, pp. 14–17. Dadda |(1965), "Some schemes for parallel multipliers," Alta Freq., vol. 34, pp.349–356. [1].

- [2].

- Z. Wang, G. A. Jullien, and W. C. Miller (1995), "A new design technique for column compression multipliers," IEEE Trans. [3]. Comput., vol. 44, no. 8, pp.962-970.

- M. Mehta, V. Parmar, and E. Swartzlander (1991), "High- speed multiple Design using multi-input counter and compressor circuit" [4]. , in Proc. 10th IEEE Symp. Comput. Arithmetic, pp.450.

- S. Veeramachaneni, L. Avinash, M. Krishna, and M. B. Srinivas (2007), "Novel Architectures for efficient (m, n) parallel counters," [5]. in Proc. 17th AC Great Lakes Symp. VLSI, pp.188-191.

- S. Veeramachaneni, K. M. Krishna, L. Avinash, S. R. Puppala, and M.B. Srinivas (2007), "Novel architectures for high-speed and [6]. low-power 3-2,4-2 and 5-2 compressors" in Proc. 20th Int. Conf. VLSI Design Held Jointly 6th Int. Conf. Embedded Syst. (VLSID), pp.324-329.

- V. G. Oklobdzija, D. Villeger, and S. S. Liu (1996), "A method for speed optimized Partial product reduction and generation of fast [7]. parallel multipliers Using an algorithmic approach," IEEE Trans. Comput., vol. 45, no. 3 pp.294-306.

- S. Asif and Y. Kong (2015), "Analysis of different architectures of counter Based Wallace multipliers," in Proc. 10th Int. Conf. [8]. Comput. Eng. Syst. (ICCES), pp.139-144.

- Anand Kumar Thangapandi, Anandharaj VijaiRavindar, Boopathy KarthikRaj, Ponnusamy Keerthana, "Design and Implementation [9]. of Symmetric Multilevel Inverter", International Journal of Advances in Computer and Electronics Engineering, Vol. 3, No. 4, pp.

- 10-14, April2018.

- [10]. Parhami B., Computer Arithmetic: Algorithms and Hardware Designs, Oxford University Press, 2000.

- [11]. G. Goto, et al., "A 4.1-ns Compact 54×54-b Multiplier Utilizing Sign-Select Booth Encoders," IEEE Journal of Solid State Circuits, vol. 32, no. 11, pp. 1676-1681, Nov.1997.

- [12]. U.Ko, P.T. Balsara, W. Lee, "Low Power Design Techniques for High Performance CMOS Adders," IEEE Transactions on VLSI Systems, vol. 3, no. 2, pp. 327-333, June1995.

- [13]. A.P. Chandrakasan, S. Sheng and R.W. Brodersen, "Low- Power CMOS Digital Design," IEEE Journal of Solid-State Circuits vol. 27, no. 4, pp.473-483.

- [14]. D. Radhakrishnan, "Low-voltage low power CMOS full adder," Proc. Inst. Elect. Eng., Circuits Devices Systems, vol. 148, no. 1, pp. 19–24,2001.

- [15]. A.M. Shams, M.A. Bayoumi, "A structured approach for designing low-power adders," Proc. 31st Asilomar Conf. Signals, Systems Computers, vol. 1, 1997, pp.757–761.

IOSR Journal of Computer Engineering (IOSR-JCE) is UGC approved Journal with Sl. No. 5019, Journal no. 49102.

S Chandrasekaran M.E" Symmetric Stacking Counter Based Testing" IOSR Journal of Computer Engineering (IOSR-JCE) 21.5 (2019): 50-57.